英特尔发力先进芯片封装 公布三项全新技术

2019-07-12 08:50 来源:英特尔

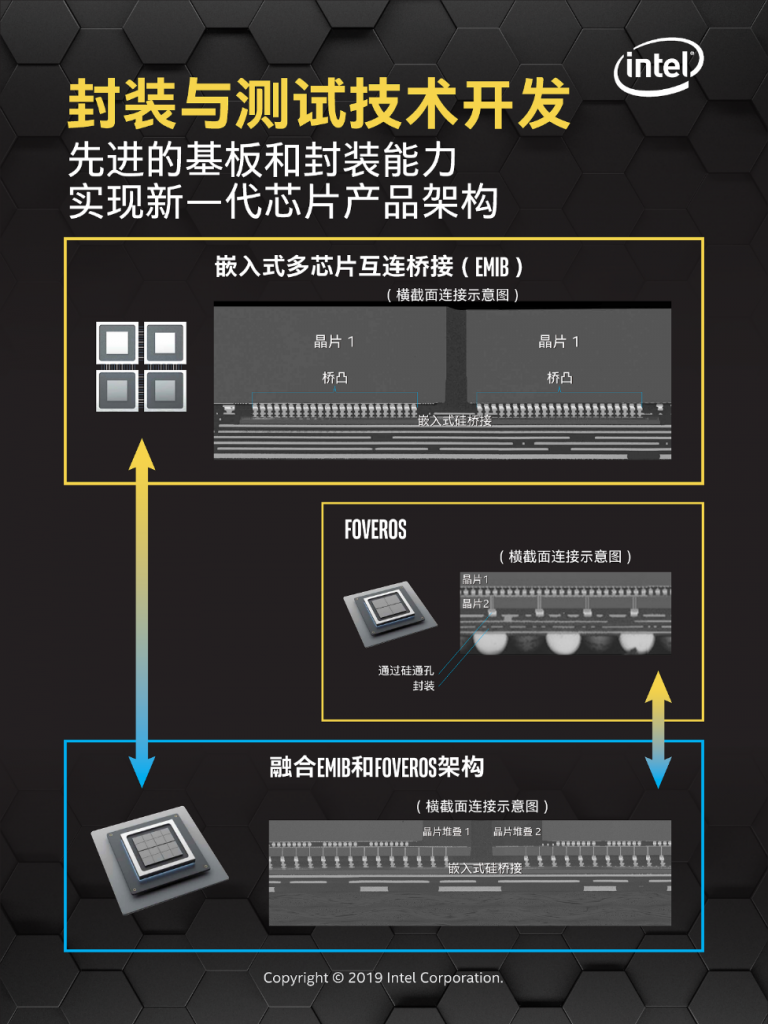

在本周于旧金山举办的 SEMICON West 大会上,英特尔的工程技术专家们介绍了英特尔先进封装技术的最新信息,并推出了一系列全新基础工具,包括将 EMIB 和 Foveros 技术相结合的创新应用,以及全新的全方位互连(ODI, Omni-Directional Interconnect)技术。英特尔的全新封装技术将与其世界级制程工艺相结合,助力客户释放创新力,走向计算新时代。

图片来源:英特尔

英特尔公司集团副总裁兼封装测试技术开发部门总经理 Babak Sabi 表示:“我们的愿景是利用先进技术将芯片和小芯片封装在一起,达到单晶片系统级芯片的性能。异构集成技术为我们的芯片架构师提供了前所未有的灵活性,使之能够在新的多元化模块中将各种 IP 和制程技术与不同的内存和 I/O 单元混搭起来。英特尔的垂直集成结构在异构集成的时代独具优势,它赋予了我们无与伦比的强大能力,让我们能够对架构、制程和封装同时进行优化,从而交付领先的产品。”

芯片封装在电子供应链中看似不起眼,却一直发挥关键作用。作为处理器和主板之间的物理接口,封装为芯片的电信号和电源提供了一个着陆区。随着电子行业正在迈向以数据为中心的时代,先进封装将比过去发挥更重大的作用。

封装不仅仅是制造过程的最后一步,它正在成为产品创新的催化剂。先进的封装技术能够集成多种制程工艺的计算引擎,实现类似于单晶片的性能,但其平台范围远远超过单晶片集成的晶片尺寸限制。这些技术将大大提高产品级性能和功效,缩小面积,同时对系统架构进行全面改造。

作为先进封装技术的领导者,英特尔能够同时提供 2D 和 3D 封装技术。在 SEMICON West 大会上,英特尔分享了三项全新技术,将为芯片产品架构开启一个全新维度。

Co-EMIB:英特尔的 EMIB(嵌入式多芯片互连桥接)2D 封装 和 Foveros 3D 封装技术利用高密度的互连技术,实现高带宽、低功耗,并实现相当有竞争力的 I/O 密度。而英特尔的全新 Co-EMIB 技术能将更高的计算性能和能力连接起来。Co-EMIB 能够让两个或多个 Foveros 元件互连,基本达到单晶片性能。设计师们还能够以非常高的带宽和非常低的功耗连接模拟器、内存和其他模块。

ODI:英特尔的全新全方位互连技术(ODI)为封装中小芯片之间的全方位互连通信提供了更大的灵活性。顶部芯片可以像 EMIB 技术下一样与其他小芯片进行水平通信,同时还可以像 Foveros 技术下一样,通过硅通孔(TSV)与下面的底部裸片进行垂直通信。ODI 利用大的垂直通孔直接从封装基板向顶部裸片供电,这种大通孔比传统的硅通孔大得多,其电阻更低,因而可提供更稳定的电力传输,同时通过堆叠实现更高带宽和更低时延。同时,这种方法减少了基底晶片中所需的硅通孔数量,为有源晶体管释放了更多的面积,并优化了裸片的尺寸。

MDIO:基于其高级接口总线(AIB)物理层互连技术,英特尔发布了一项名为 MDIO 的全新裸片间接口技术。MDIO 技术支持对小芯片 IP 模块库的模块化系统设计,能够提供更高能效,实现 AIB 技术两倍以上的响应速度和带宽密度。

图片声明:封面图片来源于英特尔官网

- 封装测试

- 严禁商业机构或公司转载,违者必究;转载请注明来源“中国闪存网”!